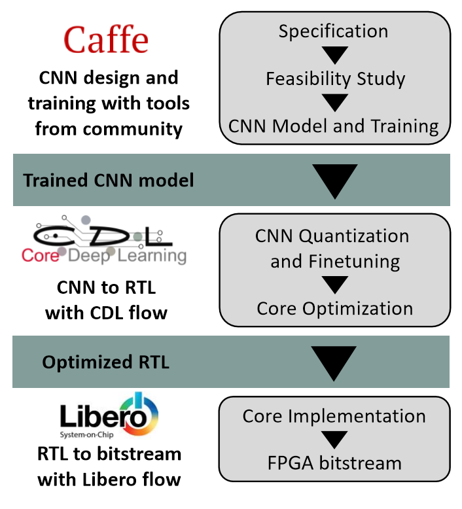

How to develop high-performance deep neural network object detection/recognition applications for FPGA-based edge devices - Blog - Company - Aldec

Deep Neural Network ASICs The Ultimate Step-By-Step Guide: Blokdyk, Gerardus: 9780655403975: Amazon.com: Books